Ansys advantage杂志

日期:2020年

弹性计算和大数据分析解决物理验证的复杂性

作者:Nitin Navale,美国圣何塞赛灵思CAD经理

更大、更复杂的硅设计正在使验证方法变得紧张,并减慢了获得结果和上市的时间。赛灵思的工程师希望利用大数据分析来简化尖端芯片的验证流程,他们希望Ansys能够提供答案。

当今许多快速发展的应用-无论是人工智能,自动驾驶汽车,基础设施还是高性能计算(HPC) -都依赖于领先的现场可编程门阵列(fpga)来实现其性能和灵活性。华体会官网app下载新浪

Xilinx XCVU440可以包含多达400个fabric子区域(FSR)实例,每个实例最多有5000个IP块实例。

硅设计趋势——以及随之而来的要求更高性能和功能的压力——向上游流向了赛灵思(Xilinx)的工程师。赛灵思是一家有着35年历史的硅谷公司,它发明了现场可编程性。由于其独特的可编程架构,fpga一直是比标准集成电路或定制系统芯片(soc)更大的设备,最近该公司的Versal ACAP产品上新功能的爆炸式增长只会使它们更大更复杂。

此外,超低电压导致极薄的噪声边界,因此可变性可能很严重。这会影响定时,其中定时延迟变化作为电压的函数随每个节点而变化。

由于具有数十亿个实例和晶体管,这些FPGA设计需要更高的容量和足够的规模和覆盖范围(比传统的动态分析和静态签名方法多50倍)才能进行适当的时序分析。如果工具能力已经有限,团队通常没有预算或时间来运行更长的模拟或更多的模拟周期来获得适当的覆盖。

其他需要考虑的问题包括2.5D和3D封装布线和技术的复杂性,如芯片片上基板(cocos),翅片场效应晶体管(finfet)的老化诱发应力,以及热和焦耳加热。此外,设计人员需要将芯片、封装和系统一起建模,以确保健全的整体电力输送网络。

应对复杂性

面对这种复杂性,Xilinx的团队已经适应了这些验证挑战。该公司采用了大数据分析和弹性计算功能,由Ansys提供支持,加快了设计的完成速度,同时准确地涵盖了芯片上可能存在显著差异的多物理场问题。

该公司的最新产品之一是Xilinx XCVU440,其中包含3000万个ASIC门。此系列中的任何产品都可以包含多达400个fabric子区域(FSR)实例,每个实例最多包含5,000个IP块实例。(FSR是仅次于完整芯片的第二大组成部分。)IP块本质上是异构的——自定义、半自定义、数字和混合信号。

硅互连技术器件在硅中间层上包含多个晶片。单个模具可以包含100到400个织物子区域(FSR)实例。FSR通常有2500到5000个IP块实例。

Xilinx在静态时序分析(STA)方面并不缺乏经验,但是现代STA正在成为一个越来越大的挑战,在更精细的过程节点上具有更大的特征复杂性。该公司需要精确的电源电压建模和更广泛的覆盖范围。由于单个芯片上有数十亿个实例和晶体管,工程师们需要一个能够扩展到足够覆盖范围的更高容量的解决方案。

传统上,为了在子区域上执行STA,设计人员会将整个芯片加载到不需要他们关注的工具和黑盒区域中。但事实证明,越来越难以分离或修剪设计的部分以进行STA,并且使用传统方法进行扩展已经开始崩溃。甚至黑盒ip也会消耗内存并影响工具性能!传统方法最适合具有很少实例的大型块,而XCVU440并不是那种庞然大物。

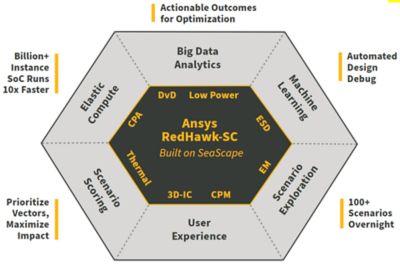

相反,该团队研究了一种子系统方法,该方法可以简化STA挑战,并在不影响准确性的情况下加快得出结果的时间。他们选择利用Ansys seasscape,这是一个专门构建的大数据平台,提供弹性计算功能和分布式文件/数据服务。seasscape可以处理大型设计,并将它们有效地分布在具有较小内存占用的较小cpu上的计算群上。从这个平台上,他们能够加载芯片并对其进行修剪,以创建STA分析的虚拟设计,该设计仅由整个设备最相关的方面组成。

随着仿真数据规模增长到难以管理的规模,赛灵思利用Ansys seasscape及其map-reduce分析来精简芯片级设计,以实现更快的时序分析。

赛灵思有一个名为时序捕获的内部过程,它不仅需要芯片的物理视图,还需要意识到它的点对点互连延迟。时序捕捉不是整个设计的时序,而是专注于高度关键的互连路径的子集。

利用ANSYS seasscape进行大型设计缩放时序分析

设计团队首先将整个芯片作为抽象的物理视图加载到seasscape中-芯片级块的DEF和SPEF(设计交换格式,标准寄生交换格式)和IP块的LEF(库交换格式)-并将其精简为仅包含下游分析所需的IP实例的精确列表。在seasscape中,他们可以很容易地删除不需要的IP实例,然后删除任何漂浮的网络。为了确保没有电容性负载丢失,所有悬挂的耦合帽都连接到虚拟攻击器上。最终视图从原始芯片的范围缩小,包含分析所需的精确IP实例,而不损失准确性。

从那里,团队可以导出经过修剪的Verilog、DEF和SPEF视图,这些视图可以加载到其他分析中。

随着仿真数据规模增长到难以管理的规模,赛灵思利用Ansys seasscape及其map-reduce分析来精简芯片级设计,以实现更快的时序分析。

Xilinx在“迷你soc”上使用单个FSR进行了一项实验,其中包含大约375,000个块实例。如果团队没有过滤它,而是按原样运行纯FSR,那么他们的STA计时器将无法处理它的大小。修剪工作由Ansys seasscape无缝管理,只需要40名seasscape工人,运行时间为6.5小时。然后,STA能够在每个角落(挂钟时间)的12小时内处理修剪后的设计。有趣的是,通过Ansys Path FX推动相同的设计,每个角落的运行时间只有一个小时(使用一个主许可证和42个工人)。

然后,该团队在一个中等规模的多fsr实验(33个fsr和3200万个区块实例)上进行了相同的测试。和以前一样,STA无法完成未修剪的设计。修剪后,STA现在以每个角落4天的挂钟时间完成。再一次,Path FX仍然更快,一天的周转时间。

该团队完成的工作是采用接近全芯片的设计版本,对其进行修剪以适应他们的STA工具,并在合理的时间内完成签字。

ANSYS RedHawk-SC:未来友好的全芯片EM/IR签名

与此同时,另一个Xilinx团队正在使用Ansys RedHawk-SC进行EM/IR签名,以查看该工具如何在相同的全芯片规模上处理复杂性和规模。EM/IR签名的目标是将芯片分割成可以在1-2 TB的主机上处理并在夜间运行的东西,最好在8小时内运行。

为了更好地把握后期技术节点设计复杂性的增加,赛灵思的16纳米UltraScale+设计可以作为一个参考点。该团队通过将整个芯片划分为七个分区来签署EM/IR,这花了大约一个人一个月的时间进行初始设置。使用eco的迭代重播大约消耗一个人一周的时间来覆盖整个芯片。为了实现相同的工具容量和分析吞吐量,7nm通用芯片需要40个分区和5倍的工程人员小时才能在相同的时间内完成。这种类型的资源投资根本无法扩展到未来。

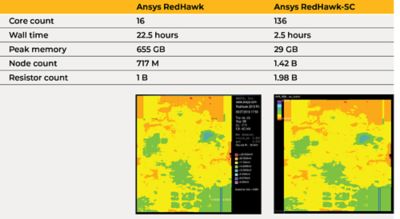

但与STA不同的是,这一次赛宁斯的工程师能够将未修剪的数据集直接输入RedHawk-SC, RedHawk-SC建立在seasscape之上,因此可以本地处理修剪。在实验中,该团队分析了一个中等大小的地点和路线块的静态IR下降(由于电阻而在输电网络中损失的直流电压),比较了四核经典红鹰和16核红鹰sc的运行。在测试用例中,经典RedHawk的挂钟时间为57分钟,而RedHawk- sc的挂钟时间为18分钟,这是一个很好的基线,可以进行进一步的比较。下一个比较测试了一个包含7800万个逻辑门的非常大的位置和路径区域-再次在两个工具中运行静态IR下降。经典的RedHawk在单个主机上最多可以达到16个核心,而RedHawk- sc在LSF farm上可以轻松扩展到136个核心。

由于RedHawk- sc将设计划分到如此多的机器或工作线程上,因此实验只需要每个工作线程29gb的峰值内存,而经典RedHawk则需要655gb的峰值内存。对比挂钟时间,红鹰sc的分布式计算在2.5小时内完成了静态分析,而经典的红鹰则需要22小时。

结果是性能有了显著的提高。RedHawk- sc实现了更快的周转和分布式计算,并且比传统的RedHawk具有更细的粒度。毫无疑问,这是EM/IR分析的未来。

ANSYS Path FX:芯片级互连延迟弹性计算

除了传统的STA Timing Closure之外,Xilinx还有一个名为Timing Capture的内部流程,该流程专门针对其全可编程架构,由该公司的Vivado软件驱动。Vivado是对芯片进行编程的工具,就像一个完整的实现流程。时序捕获不仅需要芯片的物理视图,还需要意识到它的点对点互连延迟。

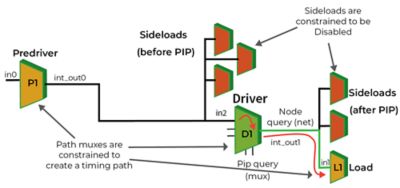

因为在编程芯片时计算这些延迟是不切实际的,所以Xilinx在设计芯片时预先计算它们,然后将延迟编程到Vivado中。因此,该工具已经意识到各种PVT角的互连时序,并在编程期间使用该时序来优化芯片。测量这些延迟的过程与传统STA中的关键路径时序分析类似。时序捕捉不是整个设计的时序,而是专注于Vivado概述的高度关键互连路径的子集。

对于传统的STA工具,必须单独处理每个冲突路径。每个冲突都意味着对更新时间的单独调用。即使对于可以组合在一起的路径,这个过程也很耗时。赛灵思希望在不牺牲精度的情况下获得更好的吞吐量和并行性。

该团队转向Ansys Path FX进行关键路径时序分析,它可以同时计算整个芯片的引脚到引脚延迟,即使在冲突的路径上也是如此。Ansys Path FX通过独立地对每条路径应用约束,然后将许多路径完全并行地分布在许多工人上,实现了这一壮举。

赛灵思Versal是一种自适应计算加速平台(ACAP),是一种新型的异构计算设备。

基于FX晶体管级仿真模型的延迟计算意味着没有精度损失。

这就是弹性计算发挥作用的地方:您可以将所有这些路径作为小型作业出租给跨LSF(负载共享设施)场的许多主机。

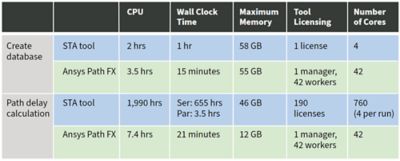

该团队在95,000条查询路径上对Path FX与传统STA签名工具的性能进行了正面测试。在测试中,在该公司值得信赖的STA工具中创建数据库需要一个小时的挂钟时间,但在内存占用(~ 55gb)相似的Path FX中只需15分钟。

下一个阶段-路径延迟计算-是路径FX真正闪耀的地方。现有的STA工具需要190个独立的工具调用和近2000个计算小时来完成所有路径的测量。时钟时间很难精确地确定,因为团队使用了许多在半并行LSF配置中运行的工具调用。在完全并行运行所有190个工具调用的最佳(也是最昂贵的)情况下,最好的挂钟时间是3.5小时。更现实的情况是,可能接近100个小时。同时,Path FX的原生并行性允许它通过单个工具调用和仅仅7.4个计算小时来完成相同的任务。Path FX的挂钟时间是21分钟。

结果大大超出了设计团队的预期。团队使用传统STA工具的半并行方法,他们已经习惯了花一周的时间完成这项工作。

Path FX的配置(一个许可证和42个工人)比传统STA工具的190个许可证更具成本效益。

大,快,准确

为了突破现代仿真瓶颈,赛灵思重新思考了其设计方法,并采用了使用Ansys工具的新方法。事实证明,这些工具可以在不牺牲时间和EM/IR分析准确性的情况下大大加快获得结果的时间。在这样做的过程中,赛灵思采用了Twitter和亚马逊(Amazon)等公司已经倡导的一种方法:大数据分析。

随着仿真数据规模增长到难以管理的规模,赛灵思利用Ansys seasscape及其map-reduce分析来精简芯片级设计,以实现更快的时序分析。同样,RedHawk-SC和Path FX使用智能修剪和分区,再加上弹性大数据计算,将每个庞大的EM/IR或互连定时作业分解为一堆小块。在后端分析的各个方面,下一代硅将依靠Ansys工具来实现。