快速的规格

Ansys Clock FX自动识别和模拟设计中的所有时钟路径,并可以解释跨多个过程、电压、温度角和场景的每条路径中导致时钟抖动的所有关键因素。

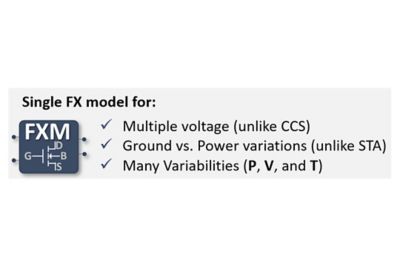

Ansys Clock FX允许您计算时钟抖动与全SoC的变化,而不采取任何捷径。其独特的单元建模为任何电压或单一库的变化条件提供SPICE精确定时。Clock FX具有全线程和分布式架构,能够扩展到数千个cpu。

Ansys Clock FX自动识别和模拟设计中的所有时钟路径,并可以解释跨多个过程、电压、温度角和场景的每条路径中导致时钟抖动的所有关键因素。

Ansys Clock FX是现有签收流程的附加组件,即使是最大的设计,也需要性能来评估SoC中的所有时钟路径的时钟抖动。

Clock FX基于时钟路径的延迟和抖动计时可以自动识别和模拟您设计中的每个时钟路径。它解释了在多个过程、电压、温度角和场景中导致时钟抖动的所有关键因素。Clock FX利用SPICE晶体管模型创建一个单一的库特性,使用全波形传播提供SPICE精度,并正确分析所有变异性影响,没有捷径。

使用独特的电压、温度和过程可变性感知单元建模的高容量spice级定时:

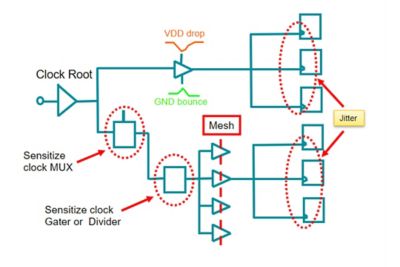

Ansys Clock FX挖掘由RedHawk-SC产生的时钟网络上的动态电压降,以spice级精度计算时钟抖动。时钟FX用于精确的多电压分析,并模拟电源变化对时钟路径的延迟影响。

Ansys Clock FX使用标准单元模型或晶体管级SPICE模型自动识别和模拟设计中的所有时钟路径。其全波形传播提供了在超低电压和先进工艺下获得可靠结果所需的精度。

Ansys Clock FX分别处理晶体管级效应,如电压降和地反弹。这使得在超低电压下能够精确定时,而超低电压的边缘非常薄,变化非常严重。

Ansys Clock FX利用SPICE晶体管模型和全波形传播提供所需的精度,以在特低电压下为高级工艺获得可靠的结果。米勒电容和其他效应被正确处理,没有捷径。

与Monte Carlo SPICE相比,Ansys Clock FX是线程化和分布式的,极大地减少了周转时间和内存需求。

Ansys Clock FX与Ansys签收功率分析工具RedHawk-SC紧密集成,可获得动态压降进行仿真。它生成一组丰富的抖动报告,涵盖各种抖动类型。