快速的规格

Ansys Exalto后lvs RLCk提取可以让IC设计人员准确预测电磁和衬底耦合效应,在之前“太大而无法分析”的电路上进行标记。提取的模型被回注到原理图或网络列表中,并支持所有电路模拟器。

Ansys Exalto是lvs后RLCk提取软件解决方案,通过提取集总元素寄生,生成电、磁和基板耦合的精确模型,使IC设计人员能够准确捕获设计层次结构中不同块之间的未知串扰。Exalto与大多数LVS工具接口,可以作为您选择的RC提取工具的补充。

Ansys Exalto后lvs RLCk提取可以让IC设计人员准确预测电磁和衬底耦合效应,在之前“太大而无法分析”的电路上进行标记。提取的模型被回注到原理图或网络列表中,并支持所有电路模拟器。

英伟达应用Ansys Raptor EM分析来降低硅上高速串行链路的风险

以前“太大而无法分析”的大型复杂电路现在可以通过Exalto的高速和高容量的硅器件EM模型来实现。

在现代硅系统中,射频和高速电路的激增已经将电磁耦合提高到一阶效应,必须精确建模才能可靠地实现硅的成功。但是,生成适合电磁耦合分析的精确寄生模型比传统的RC提取要复杂得多。这些电磁模型的尺寸给模拟器带来了挑战。

Exalto前所未有的能力使您能够轻松地分析极其复杂的布局。其独特的网表缩减方法使输出网表非常紧凑,减轻了任何模拟问题。这使得彻底分析复杂的电磁相互作用成为可能,而这些相互作用以前是通过昂贵的过度设计和防护带来避免的。结果是一个更小,更便宜的设计,更可靠的性能特征。

Exalto通过补充常规的提取工具和与所有LVS工具的无缝接口,增强了现有的设计流程。

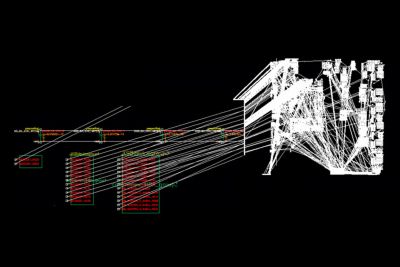

Ansys Exalto通过提取集总元素寄生,生成电、磁和基板耦合的精确模型,捕获网络和分层块之间的未知串扰。Exalto可以在不同的层次级别之间建模相声,并运行多个“假设”场景,而无需更改您的原理图。使用“指向-点击”界面,使用大型数字总线/控制信号的敏感射频电路内的复杂耦合很容易捕获。独特的网表减少方法减少输出网表超过90%。Exalto与所有LVS工具接口,并使用s参数和RLCk寄生对RC提取器进行补充,这些寄生对部分或完整的设计进行了回注释。

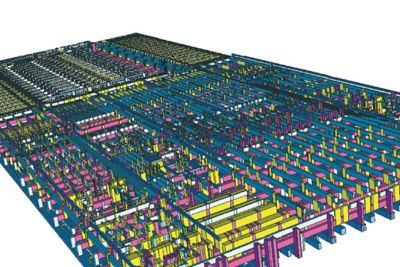

提取集总元件寄生率,为大型复杂硅电路生成精确的电、磁和衬底耦合模型

生成无源、因果直流精确s参数模型,适用于交流、谐波平衡和SP分析,以及无源、因果、高度紧凑的RLCk网表模型,适用于瞬态、射击和噪声分析。SPICE格式的RLCk网表总是可以模拟的。

Ansys Exalto可以提取叠加电感与底层器件之间的完整解析电容耦合。它利用现有的铸造特性的电容器和晶体管内部器件模型,然后只将总耦合电容集中到器件终端。Exalto具有提取全电容耦合的能力和速度,甚至可以提取数千个设备。

Ansys Exalto是建立在Ansys的建模引擎-最快的电磁引擎在行业。这意味着,一个600毫米X 400毫米,密集的7金属层电网的电磁提取需要几分钟;功率放大器中所有螺旋线到关键数字线之间的耦合模型需要几秒钟。

独特的网列表缩减方法使输出网列表非常紧凑,与本机网列表相比,元素和节点减少了90%以上。传统的RC提取器加上高频(Lk)选项会遇到容量瓶颈,因为输出网络列表太大,无法模拟。

使用不同的关键网集运行多个“假设”场景,而不接触测试台架示意图。

Ansys Exalto与第三方LVS工具无缝对接。可与第三方LPE工具的输出自动组合。Exalto还支持“提取视图”和“提取网络列表”。